# **QualiMaster**

# A configurable real-time Data Processing Infrastructure mastering autonomous Quality Adaptation

**Grant Agreement No. 619525**

# **Deliverable D3.1**

| Work-package             | WP3: Optimized Translation to Hardware                                                                                                                                                                                      |  |  |  |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Deliverable              | D3.1: Translation of Data Processing Algorithms to Hardware                                                                                                                                                                 |  |  |  |  |  |  |  |

| Deliverable Leader       | Telecommunication System Institute                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Quality Assessor         | H. Eichelberger                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Estimation of PM spent   | 6                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Dissemination level      | Public (PU)                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Delivery date in Annex I | 31/12/2014                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Actual delivery date     | 31/12/2014                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Revisions                | 4                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Status                   | Final                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Keywords:                | QualiMaster, Adaptive Pipeline, Reconfigurable Computing, FPGA Computing, Hardware, Support Vector Machines (SVM), Latent Dirichlet Analysis (LDA), Count Min, Exponential Histogram, Hayashi-Yoshida Correlation Estimator |  |  |  |  |  |  |  |

#### **Disclaimer**

This document contains material, which is under copyright of individual or several QualiMaster consortium parties, and no copying or distributing, in any form or by any means, is allowed without the prior written agreement of the owner of the property rights.

The commercial use of any information contained in this document may require a license from the proprietor of that information.

Neither the QualiMaster consortium as a whole, nor individual parties of the QualiMaster consortium warrant that the information contained in this document is suitable for use, nor that the use of the information is free from risk, and accepts no liability for loss or damage suffered by any person using this information. This document reflects only the authors' view.

The European Community is not liable for any use that may be made of the information contained herein.

© 2014 Participants in the QualiMaster Project

Page 2(of 66) www.qualimaster.eu

# **List of Authors**

| Partner Acronym | Authors                                                                                                 |

|-----------------|---------------------------------------------------------------------------------------------------------|

| TSI             | E. Sotiriades, G. Chrysos, P. Malakonakis, N. Pavlakis, S. M. Nikolakaki, I. Papaefstathiou, A. Dollas. |

| MAX             | J.B. Robertson, O. Pell                                                                                 |

| LUH             | S. Zerr                                                                                                 |

| SUH             | C. Qin                                                                                                  |

© QualiMaster Page 3(of 66)

# **Table of Contents**

|   |                   | ner                                                        |     |

|---|-------------------|------------------------------------------------------------|-----|

|   |                   | uthors                                                     |     |

|   |                   | Contents                                                   |     |

| E |                   | e summary                                                  |     |

| 1 |                   | oduction                                                   |     |

|   | 1.1               | Algorithmic classes for acceleration via Hardware          | 7   |

|   |                   | Guidelines translating algorithms to FPGAs                 |     |

|   | 1.3               | Interaction with WP2 and WP4                               | 8   |

| 2 | Iden              | tification of classes of algorithms or tasks from WP2      | . 9 |

|   | 2.1               | Reconfigurable Hardware Technology                         | 9   |

|   |                   | QualiMaster Pipeline                                       |     |

|   | 2.3               | Classes of Problems and Algorithms Selection               | 11  |

| 3 | Inter             | rface of Reconfigurable Hardware with QualiMaster Platform | 16  |

|   |                   | Maxeler Technology                                         |     |

|   |                   | Maxeler - Storm Interface                                  |     |

| 4 |                   | dy of the algorithms                                       |     |

|   |                   | Ćount-Min (CM)                                             |     |

|   |                   | Exponential Histogram (EH)                                 |     |

|   |                   | Hayashi-Yoshida Correlation Estimator                      |     |

|   |                   | SVM                                                        |     |

|   |                   | LDA                                                        |     |

|   |                   | prithm Analysis for Hardware Implementation                |     |

|   | _                 | Analysis Methodology                                       |     |

|   | 5.1.              |                                                            | 24  |

|   | 5.1.2             |                                                            |     |

|   | 5.1.3             |                                                            |     |

|   | 5.1.4             |                                                            |     |

|   |                   | Count Min (CM) Modeling                                    |     |

|   | 5.2.              | · ·                                                        |     |

|   | 5.2.2             | , i                                                        |     |

|   | 5.2.              |                                                            |     |

|   | 5.2.4             |                                                            |     |

|   |                   | Exponential Histogram (EH) Modeling                        |     |

|   | 5.3. <sup>-</sup> | · · · · · · · · · · · · · · · · · · ·                      |     |

|   | 5.3.2             | · · · · · · · · · · · · · · · · · · ·                      |     |

|   | 5.3.              |                                                            |     |

|   | 5.3.4             | · · · · · · · · · · · · · · · · · · ·                      |     |

|   |                   | Correlation Modeling                                       |     |

|   | 5.4. <sup>-</sup> |                                                            |     |

|   | 5.4.2             |                                                            |     |

|   | 5.4.              |                                                            |     |

|   | 5.4.4             |                                                            |     |

|   |                   | SVM Modeling                                               |     |

|   | 5.5. <sup>-</sup> |                                                            |     |

|   | 5.5.2             | , i                                                        |     |

|   | 5.5.3             |                                                            |     |

|   | 5.5.4             |                                                            |     |

|   |                   | LDA Modeling                                               |     |

|   | 5.6. <sup>-</sup> |                                                            |     |

|   | 5.6.2             | , i                                                        |     |

|   | 5.6.3             |                                                            |     |

|   | 5.6.4             | · · · · · · · · · · · · · · · · · · ·                      |     |

| 6 |                   | pping algorithms in Hardware                               |     |

| J | ινιαμ             | pring argonums in Haruware                                 | +U  |

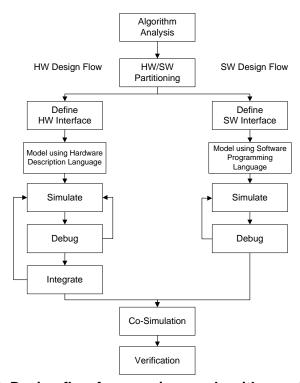

| 6.1 D     | esign Methodology                | 46 |

|-----------|----------------------------------|----|

| 6.1.1     | Top Down analysis                | 46 |

| 6.1.2     | Bottom Up Modeling               | 47 |

| 6.1.3     | Debugging Approaches             | 48 |

| 6.1.4     | Verification Issues              | 48 |

| 6.2 C     | ount Min (CM) Design             | 49 |

| 6.2.1     | Top Down analysis                | 49 |

| 6.2.2     | Bottom Up Modeling               |    |

| 6.2.3     | Debugging Issues                 | 50 |

| 6.2.4     | Verification Issues              |    |

| 6.2.5     | Performance Evaluation           |    |

| 6.3 E     | xponential Histogram (EH) Design | 50 |

| 6.3.1     | Top Down analysis                | 51 |

| 6.3.2     | Bottom Up Modeling               | 51 |

| 6.3.3     | Debugging Issues                 | 52 |

| 6.3.4     | Verification Issues              |    |

| 6.3.5     | Performance Evaluation           | 52 |

| 6.4 C     | orrelation Design                |    |

| 6.4.1     | Top Down analysis                |    |

| 6.4.2     | Bottom Up Modeling               | 53 |

| 6.4.3     | Debugging Issues                 | 54 |

| 6.4.4     | Verification Issues              |    |

| 6.4.5     | Performance Evaluation           |    |

| 6.5 S     | VM Design                        |    |

| 6.5.1     | Top Down analysis                |    |

| 6.5.2     | Bottom Up Modeling               |    |

| 6.5.3     | Debugging Issues                 |    |

| 6.5.4     | Verification Issues              |    |

| 6.5.5     | Performance Evaluation           |    |

|           | DA Design                        |    |

|           | ardware based system evaluation  |    |

| 7 Concl   | usions                           | 62 |

| Doforonce | 20                               | 62 |

# **Executive summary**

Field Programmable Gate Array (FPGA) computers (also known as reconfigurable computers) are a special category of computer hardware, in which algorithms are directly translated into hardware designs, rather than being implemented as software which runs on general purpose computers. Despite FPGA technology being almost 30 years old, the process of algorithm mapping to FPGA supercomputers is no trivial task because it entails one-of-a-kind hardware designs. In the QualiMaster project, we aim at using such FPGA-based computers as hardware accelerators offer various elements in the adaptive pipeline. This entails identification of algorithms which are suitable for hardware implementation, interfaces with existing software platforms and tools for seamless operation, hardware implementation of the chosen algorithms, and performance evaluation to quantify the performance benefits and the cost-performance tradeoffs from this approach. This deliverable reports on the methodology and the design phase of the specialized hardware of the QualiMaster adaptive pipeline for several Data Processing Algorithms and it follows Task 3.1 which comprises of three important subtasks, per the Description of Work. In the Introduction Section, below, the progress in these three subtasks is summarized, with the body of this deliverable elaborating on progress in each one of these subtasks.

Page 6(of 66) www.qualimaster.eu

### 1 Introduction

The QualiMaster project includes the use of reconfigurable hardware to boost its performance and to operate in real-time problems which conventional computers cannot address adequately. Reconfigurable computing (also known as FPGA-based computing) is the field in which algorithms are mapped directly to hardware resources for execution. As a rule-of-thumb, reconfigurable computers run at clock speeds which are ten times slower vs. conventional computers, but if the available parallelism is high and the granularity of computation vs. Input/Output requirements is high, this form of computing may offer substantial speedups vs. conventional computers. The use of this form of computing in the processing of Big Data seems promising. In the QualiMaster project the goal is to exploit reconfigurable computing in the QualiMaster pipeline, in order to have real-time processing of streaming data.

This Work Package and this deliverable D3.1 are directly connected to WP2. WP2 identifies the important classes of problems and algorithms for the QualiMaster project. In the present Deliverable D3.1 several of these algorithms, from all classes of problems, were selected for translation into hardware. Specifically, five different algorithms were selected and an in-depth study was made for each of them. This study shows that four of them are suitable for mapping at reconfigurable computers and can offer significant speedup. According to this study, the hardware designs of these algorithms were made, considering the restrictions of WP4 in which the pipeline configuration is designed.

The progress in WP3 which is reported in D3.1 can be summarized below:

#### 1.1 Algorithmic classes for acceleration via Hardware

Following extensive collaboration with all partners and especially those involved in WP2, several classes of algorithms were identified and studied. These algorithms are Support Vector Machines (SVM), Latent Dirichlet Analysis (LDA), Count Min, Exponential Histogram, and Hayashi-Yoshida Correlation Estimator. All these classes of algorithms were methodically evaluated. All of these algorithms were chosen by the software partners and studied by the hardware partners of the QualiMaster project, so that the results would be relevant to the project goals. An important contribution of the QualiMaster project is that through interaction of the software and hardware design teams of the project, the algorithms that are chosen by the software team form a real-life area in which the hardware team needs to apply its expertise, and likewise, the capabilities of the specialized reconfigurable hardware allow for the software team to have an alternative computing paradigm, which would not be possible to consider otherwise.

# 1.2 Guidelines translating algorithms to FPGAs

All of the above algorithms were profiled with respect to computational characteristics, available parallelism, Input/Output (I/O) requirements, and suitability for hardware implementation. This is the standard practice within the hardware community, as it may lead to the optimization of the computationally intensive part, or computationally equivalent mathematical transformations to lead into more hardware parallelizable versions of the algorithm. One algorithm proved to be less suitable for translation to hardware (LDA) whereas all others proved to be highly suitable (e.g. Count Min, Exponential Histogram) or moderately suitable (e.g. SVM). Subsequently, the process of developing hardware modules to interact with the software within the QualiMaster pipeline progressed.

© QualiMaster Page 7(of 66)

#### 1.3 Interaction with WP2 and WP4

Whereas this subtask is complementary to subtasks 1 and 2 (see above), it also entails the significant issue of how to connect the specialized Field Programmable Gate Array- based supercomputing nodes (made by Maxeler in this case) to the environment used by the software community in order to form a seamless QualiMaster pipeline. Following the examination of several alternatives, and in cooperation of WP2 and WP4 partners, we jointly developed the communication interfaces and libraries to make the Maxeler system become a node of the STORM distributed environment. This is a significant step which has been fully completed and is currently operational, as it allows for the QualiMaster pipeline to run seamlessly either on software platforms alone (made of distributed computational nodes) or combined software/hardware platforms, comprising of the aforementioned environment plus the Maxeler specialized hardware node. This QualiMaster platform allowed for the detailed study of communication overhead, data rates, and software/hardware interaction which was crucial in the final determination of the algorithms which are suitable for further hardware development.

This Deliverable introduces the fundamentals of reconfigurable computing, the QualiMaster pipeline, and the algorithms selection in Section 2. Section 3 presents the reconfigurable infrastructure and its integration to the rest QualiMaster infrastructure. Section 4 makes a brief presentation of the selected algorithms as they are extensively presented in D2.1. Section 5 reports the study methodology, and the studies for each of the five algorithms in order to map it to reconfigurable computing. Finally Section 6 shows how algorithms are translated to hardware designs, both in terms of the methodology and how this methodology is applied specifically on each of the selected algorithms.

Page 8(of 66) www.qualimaster.eu

# 2 Identification of classes of algorithms or tasks from WP2

# 2.1 Reconfigurable Hardware Technology

Reconfigurable Computing was introduced at the late 1980s, when the first Field Programmable Gate Arrays (FPGA) chips were designed. These chips, where the technology evolvement of the CPLDs and other older programmable devices, using different implementation technology. The main computational paradigm in this form of computing is that the hardware resources (logic gates, memories, digital signal processing – DSP blocks, etc.) are connected after power up in an application-specific way, with a design which was created earlier for that purpose. The designer maps algorithms directly to hardware, exploiting parallelism and datapaths which are not available in conventional general-purpose computing. Using even early FPGAs several computationally intensive problems have been mapped and proved that FPGA computing, or reconfigurable computing, can be a solution for performance boosting of several algorithms. Eventually, FPGAs proved not only to be a cost effective rapid system prototyping platform vs. ASIC, but a versatile technology of choice for Image Processing, Data encryption (eg. The RSA and DES algorithms), Video Processing, String Pattern Matching, FFT Implementations, Data Compression – to name a few.

Later generation devices offered significant resources in addition to the reconfigurable fabric. Special I/O transceivers, dedicated logic blocks for memory, powerful general purpose processors on chip, special modules for digital signal processing, and fast floating point operations were added on the device. Even the reconfigurable fabric had changed, offering more logic, better routing resources and run time reconfiguration characteristics. In addition, a large collection of functional Intellectual Property cores (IPs) is freely available to the designer through IP generator tools such as the Xilinx Core Generator, or, distributed by designers through web sites such as OpenCores. All these available resources help designers to take up with new applications, with considerable results on network systems such as network switches, network intrusion detection systems, financial data analysis. Data streaming applications become much more significant due to these technological advances of FPGAs, mostly in the forms of I/O transceivers on a chip and large amount of available memory.

Nowadays multi FPGA platforms have been developed offering opportunities at system level design, using powerful General Purpose Processors with fast interconnection with FPGAs. FPGAs also have ultra fast access to external memory and direct fast connection to the internet. These systems have a "look and feel" of a conventional General Purpose Server with a Linux -based operating system, using special compilers. Designers usually keep the official software at its original form and change only the computational intensive procedures, with hardware procedures calls which are functional equivalent. These servers can become nodes of greater systems, as QualiMaster projects intents, and reconfigurable computing can be easily integrated with conventional computing. The reconfigurable node performs the compute intensive parts of the algorithm and the conventional nodes perform all the other procedures which are difficult to be translated in hardware and have not significant computational load. This is considered to be a new era for reconfigurable computing which can easily incorporate heterogeneous computing systems providing them with powerful coprocessors.

# 2.2 QualiMaster Pipeline

A core concept of QualiMaster is the notion of the adaptive data processing pipeline. Basically, a data processing pipeline defines the data flow from data sources through data processing

© QualiMaster Page 9(of 66)

algorithms to data sinks. It is noteworthy that a processing pipeline defines the data flow among the elements of a pipeline rather than the control flow of the analysis algorithms.

Data sources produce data in a certain form, such as structured financial stock market data or unstructured Twitter data. While a data source can be characterized by technical information, such as the provided data fields or access credentials, an Infrastructure User (as introduced in D1.2) can also specify SLAs (Service Level Agreements) negotiated with the Data Provider to also consider deviations or violations of these agreements during adaptation. One extreme example on handling data source violations (if negotiated with the user) could be to notify the user that the SLAs on user side cannot be met as the input side does not fulfill its SLAs.

Starting at the data sources, a data processing pipeline links then data sources with data processing elements and, finally, data sinks. In QualiMaster, data processing elements exist in three types, namely elements representing processing families, generic stream processing operators and data management operations.

Processing families represent a set of algorithms performing the same task at different quality tradeoffs as described in D1.2 and detailed in D2.1 and D4.1. Changing the actual algorithm of a certain family or its functional parameter settings at runtime is the core idea of realizing adaptive data processing pipelines. Further, processing families enable the seamless integration of software-based and hardware-based execution on reconfigurable hardware. However, data processing algorithms can be more than just simple software components, e.g., representing a single processing algorithm possibly depending on a set of supporting libraries. In particular, processing algorithms can be realized in terms of reconfigurable hardware as described in this deliverable. Furthermore, a data processing algorithm can be implemented as a complex, already distributed stream processing algorithm such as the distributed correlation computation described in D2.1. Switching among these different kinds of algorithms requires specific strategies in order to consider the different functional and structural aspects as well as to use the overall resource pool in an optimal way.

Running a single algorithm on reconfigurable hardware may not be optimal for different reasons, including use of reconfigurable hardware resources, performance gain, or communication overhead. One specific optimization form is to lay out sub-pipelines of a data processing pipeline (if the translation to hardware is feasible) on the same hardware resource or within a cluster of reconfigurable hardware resources as provided by the Maxeler infrastructure (MaxelerOS). In turn, this may lead to dependencies during the design of a data processing pipeline (as the sequence must be met) as well as during its dynamic execution.

In contrast to user-defined data processing elements as handled by the processing families, generic stream processing operators, such as filter, project, fork or join are frequently considered in literature (e.g., [1, 2, 3, 4]). Generic stream processing operators can ease the adaptation (as the can be included in a domain-independent version of the QualiMaster infrastructure), simplify the definition of a data processing pipeline and facilitate reuse of generic functionality. In order to be applied, functional parameters need to be defined during the pipeline design, e.g., on what to project. These functional parameters can be specified during configuration of the pipelines. Although the QualiMaster consortium is aware of the need for such operators (e.g., D4.1 already provides an extension point for such operators), we currently focus on the more challenging user-defined processing families, handle forks and joins implicitly and will consider generic stream processing operators as part of future work.

Data Management operators as introduced in D5.1 support storing intermediary processing results for later (batch) analysis by the Data Management Layer at any point of a data processing pipeline.

Page 10(of 66) www.qualimaster.eu

As the Data Management operator is generic, it can be configured through functional parameters in order to perform the correct functionality in the actual pipeline. It is important that the data at the source and the sink may be stored transparently through the Data Management Layer in order to avoid storing the same data item multiple times by multiple pipelines.

A data processing pipeline can be considered as linear or sequential, i.e., the data flow links have data processing elements including stream forks and joins. However, if supported by the underlying Execution System, a data processing pipeline may also contain cycles in terms of feedback loops, i.e., processed data is fed back into a previous processing step, e.g., to improve the processing model. In this case, a data processing pipeline can be considered as a data processing network or graph.

The design of a data processing pipeline may specify quality constraints on the individual data processing elements, e.g., to guard extremely important processing steps as well as on data flows to provide guidelines for switching among explicit alternatives. In QualiMaster, These constraints fulfill two purposes, the first supporting the user, the second the QualiMaster consortium. On the user side, such constraints allow narrowing down the adaptation space and, if needed to specify explicit alternatives to be taken dynamically based on the constraint. However, we are aware of the fact that specifying constraints increases the specification effort and requires more knowledge about data processing. Thus, we focus currently more on the processing families rather than on the pipeline constraints. On the other side such constraints allow to change the scope of experiments, i.e., using a pipeline specification for multiple purposes by just modifying some experiment-specific settings.

Ultimately, the data produced by the entire data processing pipeline is directed to data sinks, i.e., the endpoints of a data processing pipeline. Multiple data sinks may provide different forms or qualities of output, e.g., data sinks may offer different levels of quality and, depending on the business model of the infrastructure/data analysis provider, possibly also at different levels of pricing. Akin to data sources, data sinks can be detailed by SLAs in order to reflect the negotiated client side quality. Further, data sources may be supplemented with technical access information, e.g., in order to protect the output data as well as different levels of result quality. Finally, a kind of web service realizes the data sink from a technical perspective in order to make the data available to the QualiMaster applications. Thereby, the (realization of the) data sink will not act as a one-way service, as it needs to provide an interface to communicate with the QualiMaster infrastructure, in particular to react on user triggers to be considered by the adaptation (see D1.2).

# 2.3 Classes of Problems and Algorithms Selection

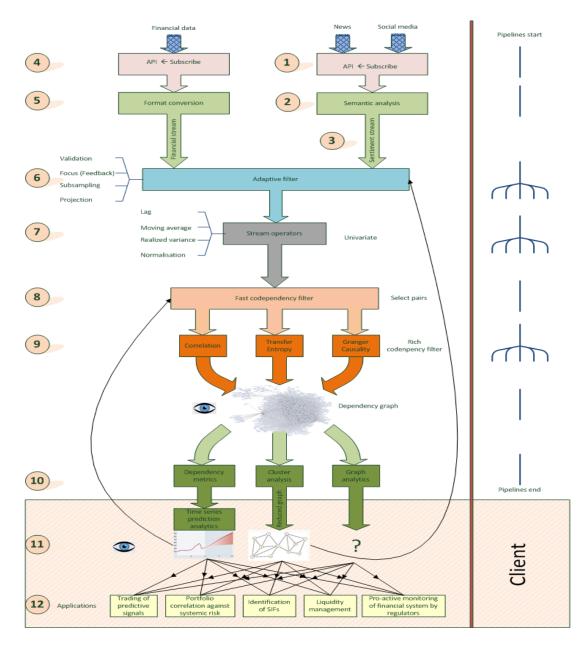

Data processing with the QualiMaster pipelines includes several different steps, as shown in Figure 1 describes a possible execution scheme of the QualiMaster pipeline, as it was presented in D 1.1. Most of the computational elements shown in this Figure can be efficiently mapped to hardware. Data Reformatting, Data Filtering, Data Classification, Streaming Computation, Correlation, Transfer Entropy, Granger Causality, Data Clustering, Graph Analysis, Data Synopsis and Sentimental Analysis are classes of problems that have been mapped efficiently to reconfigurable hardware and have been reported in the relevant literature on several occasions. However, this does not make the integration of the reconfigurable hardware with the software an easy task. The implementation of single computational elements with reconfigurable computing resources, as reported in the literature, not only is based on specific assumptions regarding Input/Output, dataset size, and algorithm accuracy, to name a few, but even if such were not significant issues (and they are), the QualiMaster project needs to address effective use of the specialized reconfigurable hardware resources in order to optimize the entire pipeline. To illustrate,

© QualiMaster Page 11(of 66)

two possible scenarios in which the end result would lead to a slowdown at the system level are presented.

Scenario A: if algorithm A runs exceptionally well on reconfigurable hardware (e.g. 100 times faster than software execution of the same algorithm) but it expects results from algorithm B which runs on software, and algorithm B does not produce data at a sufficiently high rate, then not only the potential of the reconfigurable hardware is not realized, but the Input/Output time overhead to move data in and out of the reconfigurable hardware may dominate over the computational time benefits, leading to an actual slowdown. Referring to Figure 1, if the Fast Codepedency Filter (see step 8) is run in software and Correlation (see step 9) is run in reconfigurable hardware, the overall performance of the QualiMaster pipeline will not only depend on the performance of the individual elements of the pipeline, but also their integration.

Scenario B: If separate elements of the pipeline run well on the hardware, it is possible that it is beneficial to run non-optimal elements as well, in order to avoid Input/Output overhead. Continuing from scenario A, if in order to address the problems which were describe above we run forth the Fast Codependency Filter and the Correlation in hardware, it is possible that we will also need to run in hardware the Transfer Entropy and the Element Causality as well (both are in Step 8 of the pipeline), in order to avoid excessive Input/Output of the (partial in this case) results of the Fast Codependency Filter and Correlation pipeline from having to be forwarded to software, potentially causing an Input/Output bottleneck. However, even in this case, it is not clear that the hardware has enough resources to run all of the above.

As a result from the considerations, above, different elements of the QualiMaster pipeline need to be implemented in hardware, benchmarked, and evaluated vis a vis the same elements running on software, so that there will be a system-level optimization. The only way to achieve this goal is to have many different potential implementations of the QualiMaster pipeline and many different forms of data (e.g. twitter, financial data), as the optimal solution in one case might be undesirable in another. Hence the QualiMaster pipeline will be truly adaptive to the workload, desired processing algorithms, and available hardware resources (in principle there can be more than one reconfigurable hardware nodes in the system).

In this context, WP3 interacted with WP2, in order to find out the classes of problems and the algorithms which are relevant for QualiMaster, in particular in the context of the priority pipeline reconfigurable platform elements. The algorithm families of interest are identified as:

- Data Classification

- Sentiment Analysis

- Data Synopsis

- Correlation Estimation

The above classes of problems seem to be closely connected to the goals of the QualiMaster project. The above problems are very computationally intensive, thus the acceleration of these workloads would be a benefit to the final QualiMaster infrastructure. There is substantial related work on similar classes of problems, where hardware-based accelerators have been proposed. Several algorithms were proposed in collaboration with WP2 for each class of desirable algorithms.

Data Classification aims at categorizing data objects into distinct classes with the use of labels. In particular, statistical classification receives new data inputs and identifies their respective classes. An example would be assigning a post derived from the social media into "relevant or "irrelevant"

Page 12(of 66) www.qualimaster.eu

classes based on its correlation with a general subject, i.e. finance, news, or social. Given that the scope of the project is to receive Twitter data with a view of performing efficient risk and Sentiment Analysis, categorizing streamed text information for its effective use is crucial for QualiMaster. In addition, Sentiment Analysis refers to the use of natural language processing and text analysis to identify and extract subjective information from source materials. In the QualiMaster project extracting sensible and related to financial knowledge is significant for precise and accurate risk analysis. Furthermore, Data Synopsis focuses on configuring data structures and algorithms for efficiently processing and storing massive datasets or swiftly arriving data. The use of synopses allows fast response times to queries on big datasets, a function necessary to QualiMaster as efficient handling of streaming financial data (commodities) is essential. Finally, Correlation Estimation is a method that reports the dependence between two random variables. Thus, in QualiMaster correlation is used to determine the dependence between commodities.

Implementing our own text classifiers by hand would be time-consuming and could be quite difficult. In general, text comprises several aspects that need to be taken into consideration, such as the high dimensional input space, linearly separability and few irrelevant features. Thus, in accordance with WP2 and by studying the related literature we concluded that the Support Vector Machines (SVM) method is appropriate for text classification.

Various machine learning algorithms, which are used for data regression and classification, have been introduced at D 2.1 and proposed for hardware acceleration. We studied thoroughly the algorithms about Linear Regression, Bayesian Linear Regression, Support Vector Machines and Linear Generative Classification. The Support Vector Machines (SVM) algorithm was selected as the most common one and with parallel processing characteristics to be implemented for the data classification problem.

© QualiMaster Page 13(of 66)

Figure 1: QualiMaster pipeline example execution steps

For the sentiment analysis the LDA algorithm was chosen to be implemented in hardware, and more specifically its training phase as it is the most time consuming part of the algorithm. LDA is an algorithm used in order to classify a set of documents into topics. The topics can contain opinion targets as well as the polarity of the opinion. This allows sentiment analysis to exact information about the main theme of the document, as well as polarity, by examining the topics it is associated with (taking into account the probabilities for each topic). Topic modeling is a basic step for the sentiment analysis of documents. Moreover, topic modeling is a common method, which is used in machine learning and natural language processing. Atopic model is a type of statistical model for discovering the abstract "topics" that occur in a collection of documents. The most widely used algorithm is LDA, which is also the one used by WP2. In LDA algorithm, each document may be viewed as a mixture of various topics. This is similar to probabilistic latent semantic analysis (pLSA). In addition, the topic distribution in LDA algorithm is assumed to have a Dirichlet prior probability distribution. In practice, this results to more reasonable mixtures of topics in a document.

Page 14(of 66) www.qualimaster.eu

The large volume of data streams poses unique space and time constraints on the computation process. There are problems that may be acceptable to generate approximate solutions for problems with streaming huge volumes of data. A number of synopsis structures have been developed, which can be used in conjunction with a variety of mining and query processing techniques in data stream processing. Sketches are one of the simplest data structures that are used for data synopses. Count-Min sketch is a probabilistic data structure that serves as a frequency table of events in a stream of data. Another basic data structure, which is used for data synopsis, is the histogram. There is a great variety of algorithms that create histogram data synopsis from streaming data. Exponential Histograms is an efficient data structure that enables answering frequency queries over streaming data. In addition, the ECM sketch is a data structure that combines the CM sketch with the Exponential Histogram data structure to an application for efficient querying over sliding window data streams. The ECM is considered to be a more sophisticated way of data synopsis. As the ECM method is a combination of the Count-Min algorithm and the Exponential Histogram data structure both of them were proposed to be developed. Lastly, these implementations will be combined in order to implement the efficient mapping of the ECM sketch on reconfigurable hardware. The ECM method takes as input a stream of elements and updates the corresponding CM sketch data structure. The CM sketch is updated by keeping an order-preserving aggregation of all streams. The update of the data structure takes place in different buckets of the data structure thus it needs a lot of CPU clock cycles in order to be updated. According to the theory the update of the ECM has O(1) amortized time complexity. A pipelined reconfigurable system that maps the update function will offer O(1) time complexity in any case. In addition, the small memory footprint of the CM data structure leads to a system that maps such data structure internally in an FPGA device offering high throughput in case of CM updating or CM querying.

One of the main goals of the QualiMaster project is the use of methods that will monitor data streams for event detection. A statistical technique that can show whether and how strongly pairs of variables are related is the correlation measure. In the world of finance, financial correlations measure the relationship between the changes of two or more financial variables, e.g. stock prices, in time. Financial correlation measurements are considered very important and they are used in advance portfolio management. The Hayashi-Yoshida cross-correlation estimator is an important estimator of the linear correlation coefficient between two asynchronous diffusive processes, e.g. stock market transactions. This method is really important as it can correlate high-frequency financial assets. Also, the Hayashi-Yoshida estimator correlates the variables, e.g. the stock prices, in real time, which is really important for forecasting the mid quote variation of the corresponding values. Lastly, the Hayashi-Yoshida estimator is considered as one of the most important and most basic estimators over streaming data, thus was proposed for implementation at the QualiMaster Use Cases as they have indicated at D1.1.

The correlation matrix algorithm can calculate the correlation between multiple commodities in parallel. Also, the calculation of a single correlation estimator can be processed in parallel using the corresponding data. Reconfigurable hardware can offer high parallelization levels by using different resources in parallel or/and in a pipelined architecture.

© QualiMaster Page 15(of 66)

# 3 Interface of Reconfigurable Hardware with QualiMaster Platform

In this section there is a short description of the target platform (a Maxeler C-Series FPGA-based supercomputing node) for the algorithms mapped to hardware and the interface with the project platform (Storm) which is the framework for the project.

# 3.1 Maxeler Technology

Maximum Performance Computing (MPC) changes the classical computer science optimization from ease-of-programming to maximizing performance and minimizing total cost of computing. Performance is optimized by constructing compute engines to generate one result per clock cycle, wherever possible. Ease-of-programming is still important but takes second place to performance, computational density and power consumption. As such, MPC focuses on mission critical, long running computations with large datasets and complex numerical and intense statistical content. Maxeler drives MPC via 'Multiscale Dataflow Computing'. This section summarises the components of MPC, illustrates how MPC dataflow computers are programmed and how the resulting tools are presented to the users. An overview of MPC, along with detailed examples of applications, is available in [27, 28].

One Maxeler Dataflow Engine (DFE) combines 10<sup>4</sup> arithmetic units with 10<sup>7</sup> bytes of local fast SRAM and 10<sup>1</sup> bytes of 6-channel large DRAM. MaxelerOS allows the DFEs and CPU to run in parallel, so while the DFEs are processing the data, the CPU typically performs the non-time-critical parts of an application.

Maxeler's MPC programming environment comprises of several components:

- MaxCompiler, a meta-programming library used to produce DFE configurations by way of the MaxJ programming language, which is an extended form of Java with operator overloading. The compute kernels handling the data-intensive part of the application and the associated manager, which orchestrates data movement within the DFE, are written using this language. MaxJ is a Hardware Description language which produces the computational intensive part of the design configuration.

- the SLiC (Simple Live CPU) interface, which is Maxeler's application programming interface for CPU-DFE integration;

- MaxelerOS, a software layer between the SLiC interface, operating system and hardware, which manages DFE hardware and CPU-DFE communication in a way transparent to the user;

- MaxIDE, a specialised integrated development environment for MaxJ and DFE design, a fast DFE software simulator and a comprehensive debug environment used during development.

These components and their use are described in details in [29, 30].

In such an MPC system, the CPUs are in control and drive the computations on the DFEs. The data-intensive parts of the computations are typically confined to the DFE configuration and are made available through the SLiC interface. At its simplest level, DFE computation can be added to an application with a single function call, while for more fine-grained control SLiC provides an "action"-based interface. SLiC interface calls are automatically generated from the corresponding DFE program pieces and allow DFE programs to be used by a range of programming languages including C/C++ or R, Python, and MATLAB by way of a adaptation layer (or skin). Thanks to

Page 16(of 66) www.qualimaster.eu

MaxelerOS's seamless management of DFE resources, these programming languages may make use the DFE program as they would make use of any other external library or service.

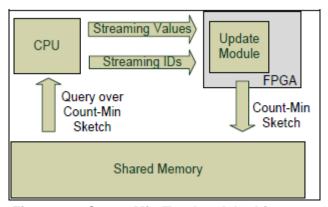

#### 3.2 Maxeler - Storm Interface

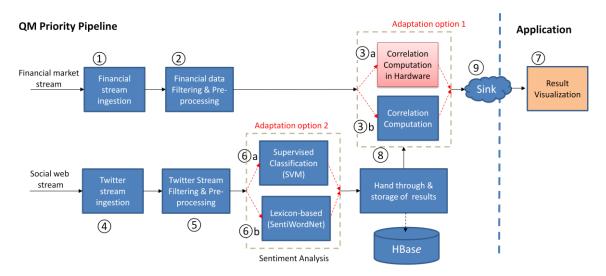

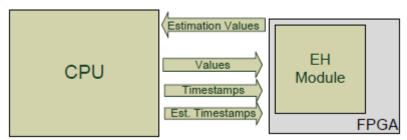

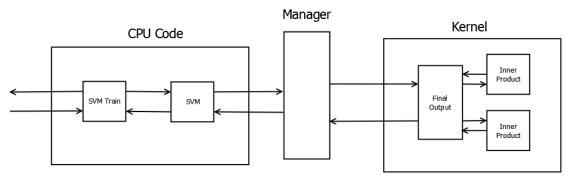

The integration of reconfigurable hardware (e.g. Maxeler machines) along with the QualiMaster infrastructure plays an essential role. A communication framework needed to be created so that the reconfigurable hardware could receive data, make any calculations needed, and then transmit the results back to rest of the infrastructure. At D5.2 the QualiMaster infrastructure and priority pipeline are describe. Figure 2 depicts the QualiMaster priority pipeline, where the Adaptation Layer may decide to execute 3a or 3b depending on the configuration and monitoring of the pipeline execution. Hence, 3a needs to implement the communication framework between the QualiMaster pipeline and the reconfigurable hardware. Basically it involves the implementation of a flexible interface between Storm and Maxeler, which could be also used with different tools or reconfigurable hardware platforms.

Figure 2: QualiMaster Infrastructure-Reconfigurable Hardware Integration (from D5.2)

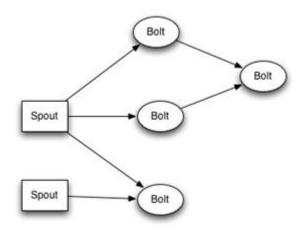

In order to initiate Storm [31] the Adaptation Layer creates topologies. A Storm topology is a graph of computation. Each node in a topology contains processing logic, and links between nodes indicate how data should be passed around between nodes. The core abstraction in Storm is the "stream". A stream is an unbounded sequence of tuples. Storm provides the primitives for transforming a stream into a new stream in a distributed and reliable way.

The basic primitives Storm provides for doing stream transformations are "spouts" and "bolts". Spouts and bolts have interfaces that are implemented to run application-specific logic. A spout is a source of streams. For example, a spout may connect to the Twitter API and emit a stream of tweets. A bolt consumes any number of input streams, does some processing, and possibly emits new streams. Complex stream transformations, like computing a stream of trending topics from a stream of tweets, require multiple steps and thus multiple bolts. Bolts can do anything from run functions, filter tuples, do streaming aggregations, do streaming joins, talk to databases, and more.

Networks of spouts and bolts are packaged into a "topology" which is the top-level abstraction that is submitted to Storm clusters for execution. A topology is a graph of stream transformations where each node is a spout or bolt. Edges in the graph indicate which bolts are subscribing to which streams. When a spout or bolt emits a tuple to a stream, it sends the tuple to every bolt that subscribed to that stream.

© QualiMaster Page 17(of 66)

Figure 3: Storm Topology

Each node in a Storm topology, Figure 3, executes in parallel. In the topology, the amount of parallelisms specified, and then Storm will spawn that number of threads across the cluster to do the execution. A topology runs forever, or until the user kills it. Storm will automatically reassign any failed tasks. Additionally, Storm guarantees that there will be no data loss, even if machines go down and messages are dropped.

The Storm framework was installed on the Maxeler workstation and was tested as a simple Storm node. After that the connection with the Maxeler hardware had to be established. The Maxeler hardware is called by a C/C++ host code. The main problem that had to be addressed is basically the interface between Java (Storm) and C. Three methods that allow C/C++ and Java connection were considered, SWIG that allows the call of C function through Java, the exec function which calls the C executable and network sockets.

In order to use SWIG to connect the Storm Java code with C the Maxeler project was compiled as a shared library. SWIG (Simplified Wrapper and Interface Generator) [32]is a software development tool that connects programs written in C and C++ with a variety of high-level programming languages. SWIG is used with different types of target languages including common scripting languages such as Javascript, Perl, PHP, Python, Tcl and Ruby. The list of supported languages also includes non-scripting languages such as C#, Common Lisp (CLISP, Allegro CL, CFFI, UFFI), D, Go language, Java including Android, Lua, Modula-3, OCAML, Octave and R. SWIG is most commonly used to create high-level interpreted or compiled programming environments, user interfaces, and as a tool for testing and prototyping C/C++ software. SWIG is typically used to parse C/C++ interfaces and generate the 'glue code' required for the above target languages to call into the C/C++ code. After wrapping the C code with SWIG the C function can be called as a native code call from the Java. The problem was that in order to use SWIG, its' data types had to be used in order to be able to exchange arguments from C to Java.

The exec in Java is able to directly call the Maxeler executable. The exec function takes as arguments the executable file along with the arguments needed. Also a custom scheduler would have to be implemented in order to send the specific Java code (with the exec call) to the Maxeler workstation.

The first method proposed was the use of network sockets [33] in order to establish communication between the Java code and the C host code running on the Maxeler workstation. The Maxeler server creates sockets on start up that are in listening state. These sockets are

Page 18(of 66) www.qualimaster.eu

waiting for initiatives from client programs (e.g. Storm nodes). A TCP server may serve several clients concurrently, by creating a child process for each client and establishing a TCP connection between the child process and the client. Unique dedicated sockets are created for each connection. These are in established state, when a socket-to-socket virtual connection or virtual circuit (VC), also known as a TCP session, is established with the remote socket, providing a duplex byte stream. We can have up to 4 children on a Maxeler workstation as they can have 4 different hardware designs running simultaneously on the 4 FPGAs.

Two socket clients are used in order to make a call on the hardware server, a transmitter and a receiver. They are written in Java and run on a Storm subtopology (3a), which implements the appropriate algorithmic family interface. The transmitter creates a new socket in order to connect to the server and sends the configuration as well as the input data from previous components. The transmitter can also request for the results to be sent to the receiver. The receiver is connected via a different socket. It receives the results and forwards them to the rest of the pipeline. The socket server is written in C and serves as the Maxeler host code. It stays on listening state until a connection is established by both a transmitter client and a receiver client. The transmitter streams configuration and input data to the server. The server stores the data coming from the transmitter and performs the Maxeler hardware call to process them. After the hardware call has returned, it sends the results to the receiver client whenever a result request is received. The receiver and transmitter libraries can also be used outside Storm, which provides even more flexibility.

The three methods were compared in terms of flexibility and functionality. The use of SWIG basically reduces the flexibility of the interface, as the Java code would have to be rewritten using SWIG's data types. The exec function allows more flexibility as only a function call would have to be included in the Java code, but even though it worked perfectly when called by Java on the workstation, it didn't work if the code came through Storm. The network sockets approach was chosen, because they are flexible as they can be used by any tool that can implement sockets. Also sockets are faster as there is no need of interface functions (SWIG) or system calls (exec). The only drawback is that socket connections have to be opened on the client side (e.g. Java sockets), while exec or a native function call would be simpler.

© QualiMaster Page 19(of 66)

# 4 Study of the algorithms

In this section the algorithms that have been selected are presented. The descriptions of the algorithms is more detailed in WP2 and we recapitulate important aspects for our work in this deliverable. This section has been added for reason of completeness of the deliverable.

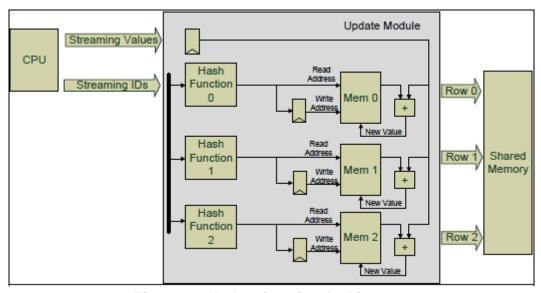

# 4.1 Count-Min (CM)

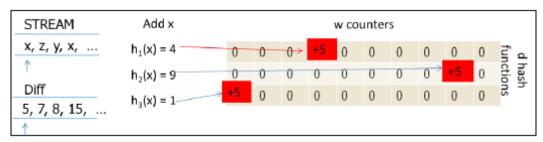

The QualiMaster project focuses on the development of novel approaches that deals with largescale data streaming. The Count-Min sketch is a popular and simple algorithm for summarizing data streams by providing decent summary statistics. The Count-Min data structure can be used in terms of the QualiMaster project for handling multiple and high-frequency large datasets in the proposed data processing settings with surprisingly strong accuracy. Count-Min [41] sketches are a widely applied sketching technique for data streams. A Count-Min sketch is composed of a set of d hash functions,  $h_1(.), h_2(.), ..., h_d(.)$ , and a 2-dimensional array of counters of width w and depth d. Hash function h<sub>i</sub> corresponds to row j of the array, mapping stream items to the range of [1... w]. Let CM[i,j] denote the counter at position (i,j) in the array. To add an item x of value  $v_x$  in the Count-Min sketch, we increase the counters located at CM[ $h_i(x)$ , j] by  $v_x$ , for  $j \in [1 ... d]$ . A point query for an item q is answered by hashing the item in each of the d rows and getting the minimum value of the corresponding cells. Note that hash collisions may cause estimation inaccuracies only overestimations. By setting  $d=[\ln(1/\delta)]$  and  $w=[e/\epsilon]$ , where e is the base of the natural logarithm, the structure enables point queries to be answered with an error of less than e||a||1, with a probability of at least 1-δ, where ||a||<sub>1</sub> denotes the number of items seen in the stream. Similar results hold for range and inner product queries.

The goal of parallelizing the Count-Min algorithm and mapping it on a reconfigurable platform is the improvement of both the result quality and the processing times. In any skech-based sequential algorithm, the most expensive operations are the update and querying of the sketch data structure as it is updated for every item in the stream. To achieve scalability, our FPGA-based solution tries to accelerate these operations.

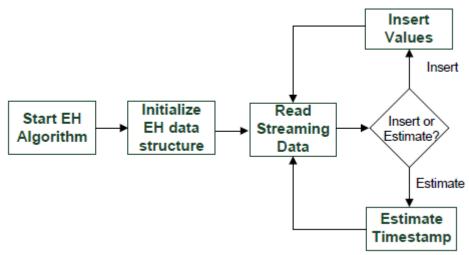

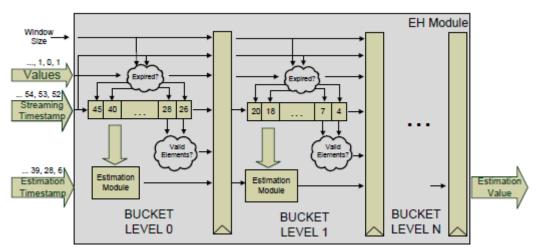

# 4.2 Exponential Histogram (EH)

The QualiMaster project focuses on processing of streams that come from different and distributed data sources. In addition, the goal of the QualiMaster is the efficient processing of huge amounts of data over time-based sliding windows. Exponential histograms (EHs) [17] guarantee complex query answering over distributed data streams in the sliding-window model. The use of EHs in the QualiMaster project would offer fast answering queries over distributed streams and efficient storage of the statistics over sliding windows. Exponential histograms [17] are a deterministic structure, proposed to address the basic counting problem, i.e., for counting the number of true bits in the last N stream arrivals. They belong to the family of methods that break the sliding window range into smaller windows, called buckets or basic windows, to enable efficient maintenance of the statistics. Each bucket contains the aggregate statistics, i.e., number of arrivals and bucket bounds, for the corresponding sub-range. Buckets that no longer overlap with the sliding window are expired and discarded from the structure. To compute an aggregate over the whole (or a part of) sliding window, the statistics from all buckets overlapping with the guery range are aggregated. For example, for basic counting, aggregation is a summation of the number of true bits in the buckets. A possible estimation error can be introduced due to the oldest bucket inside the query range, which usually has only a partial overlap with the query. Therefore, the maximum possible estimation error is bounded by the size of the last bucket.

Page 20(of 66) www.qualimaster.eu

To reduce the space requirements, exponential histograms maintain buckets of exponentially increasing sizes. Bucket boundaries are chosen such that the ratio of the size of each bucket b with the sum of the sizes of all buckets more recent than b is upper bounded. In particular, the following invariant (1) is maintained for all buckets j:

$$C_j/(2(1+\sum_{i=1}^{j-1}C_i)) \le e(1)$$

where e denotes the maximum acceptable relative error and Cj denotes the size of bucket j (number of true bits arrived in the bucket range), with bucket 1 being the most recent bucket. Queries are answered by summing the sizes of all buckets that fully overlap the query range, and half of the size of the oldest bucket, if it partially overlaps the query. The estimation error is solely contained in the oldest bucket, and is therefore bounded by this invariant, resulting to a maximum relative error of e.

The EHs access each data element at its arriving time and needs to be processed in real time. This constraint can be really challenging to be satisfied especially when there are irregularities and bursts data arrival rates. This problem is mainly due to insufficient time for the underlying CPU to process all stream elements or due to the memory bottleneck to process the queries. The Qualimaster project focused on the mapping of the EH data structure on reconfigurable hardware in order to develop new hardware-accelerated solutions that can offer improved processing power and memory bandwidth to keep up with the update rate.

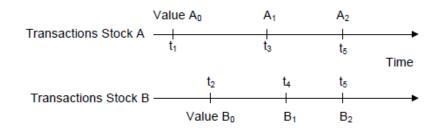

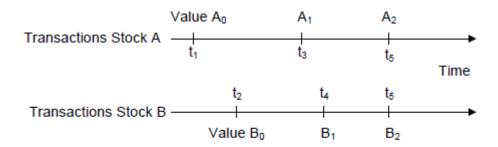

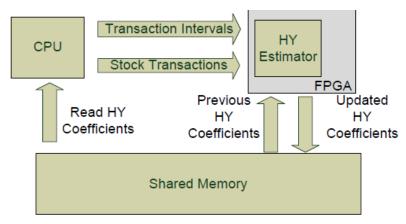

#### 4.3 Hayashi-Yoshida Correlation Estimator

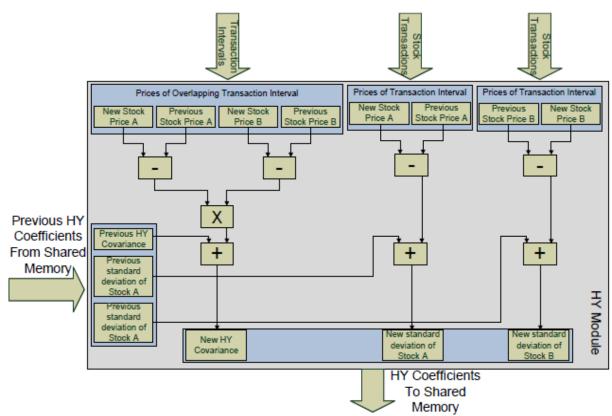

One of the objectives for the QualiMaster project is the implementation of a platform that processes in real time financial data. The financial data can arrive in a non-synchronous way, thus the processing of such data streams is a really critical issue. The covariance among the prices of the market stocks plays a crucial role in modern finance. For instance, the covariance matrix and its inverse are the key statistics in portfolio optimization and risk management. There are two crucial points pertaining to practical implementation of computing correlation over streaming data. First, the actual transaction data is recorded at non-synchronous times. The covariance estimator calculation is, usually, based on regularly spaced synchronous data but this can lead to unreliable estimation due to the problematic choice of regular interval and the data interpolation scheme. Second, a significant portion of the original data sets could be missing at pre-specified grid points due to such randomness of spacing. Thus, the correlation would lead to unreliable results. One of the most efficient correlation estimators is the Hayashi-Yoshida Correlation Estimator. The proposed method does not require any prior synchronization of the transaction-based data. The Hayashi-Yoshida covariance estimator is defined as follows:

$$HYcov = \sum_{i,j} \left( P_{t_i}^1 - P_{t_{i-1}}^1 \right) * \left( P_{t_j}^2 - P_{t_{j-1}}^2 \right) * 1_{\left\{ [t_i, t_{i-1}] \cap [t_j, t_{j-1}] \neq \emptyset \right\}} \quad (1)$$

where  $P_{t_i}^1$ ,  $P_{t_{i-1}}^1$  the values of variable 1 at times  $t_i$ ,  $t_{i-1}$ , respectively, and  $P_{t_i}^2$ ,  $P_{t_{i-1}}^2$  the values of variable 2 at times  $t_j$ ,  $t_{j-1}$ , respectively

Eq. 1 uses the product of any pair of increments that will contribute to the sum only when the respective observation intervals are overlapping with each other. The Hayashi-Yoshida covariance estimator is consistent and unbiased as the observation time intensity increases to infinity. Using

© QualiMaster Page 21(of 66)

the Hayashi-Yoshida covariance estimation Eq. 1, the proposed non-synchronous correlation estimator is computed by the Eq. 2.

$$HYcor = \frac{\sum_{i,j} (P_{t_i}^1 - P_{t_{i-1}}^1) * (P_{t_j}^2 - P_{t_{j-1}}^2) * 1_{\{[t_i, t_{i-1}] \cap [t_j, t_{j-1}] \neq \emptyset\}}}{\sqrt{\sum_i (P_{t_i}^1 - P_{t_{i-1}}^1)^2 * \sum_j (P_{t_j}^2 - P_{t_{j-1}}^2)^2}}$$

(2)

where  $P_{t_i}^1, P_{t_{i-1}}^1$  the values of variable 1 at times  $t_i, t_{i-1}$ , respectively, and  $P_{t_j}^2, P_{t_{j-1}}^2$  the values of variable 2 at times  $t_j, t_{j-1}$ , respectively.

The quantities at the denominator represent the realized volatilities calculated using raw data. As shown in Eq. 2, the calculation of the Hayashi-Yoshida Correlation Estimator can be easily parallelized. Also, the reconfigurable hardware offers high parallelization level in order to calculate in parallel the correlation estimator among different stock markets.

#### 4.4 SVM

The QualiMaster project exploits data derived from Twitter, in order to achieve risk analysis of financial data. Therefore sentiment analysis is a significant procedure of the project which is achieved with the SVM classification method as the specific method has yielded remarkable results in this area. In particular, Support vector machines (SVMs) were introduced by Vapnik et al. [6, 7] and they are considered to be highly accurate methods for a various set of classification tasks [5, 8, 9, 10]. Manning et al. [11] presented a work that uses SVM method for text classification. The algorithm takes as input a set of n training documents with the corresponding class labels and trains the SVM model. The linear SVM method aims at finding a hyperplane that separates the set of positive training documents from the set of negative documents with a maximum margin. The separating hyperplane, i.e. decision hyperplane[11] or decision surface [12], takes the "decision" for separating the input documents. However, Bernhard E. Boseretal. suggested a way to create nonlinear classifiers by applying the kernel trick (originally proposed by Aizermanetal. [13]) to maximum-margin hyperplanes [14]. The final algorithm is similar to the initial; apart from that every dot product is replaced by a nonlinear kernel function. This allows the algorithm to fit the maximum-margin hyperplane in a transformed feature space, and thereby achieving linear separation. The transformation may be nonlinear and the transformed space high dimensional. Thus, despite the fact the classifier can be a hyperplane in the high-dimensional feature space; it may be nonlinear in the original input space.

Furthermore, given training vectors  $x_i \in R^n$ , i = 1, ..., I, in two classes, and an indicator vector  $y_i \in R^I$ , such that  $y_i \in \{1,-1\}$  that represents the respective labels, SVM solves the following dual optimization problem:

$$\min_{\boldsymbol{\alpha}} \quad \frac{1}{2} \boldsymbol{\alpha}^T Q \boldsymbol{\alpha}$$

subject to  $0 \le \alpha_i \le 1/l, \quad i = 1, \dots, l,$

$$\boldsymbol{e}^T \boldsymbol{\alpha} \ge \nu, \quad \boldsymbol{y}^T \boldsymbol{\alpha} = 0,$$

In this problem,  $Q = y_i y_j K(x_i, x_j)$ , where  $K(x_i, x_j)$  is the kernel and  $e = [1, ..., 1]^T$  is a the vector of all ones.

Page 22(of 66) www.qualimaster.eu

Traditionally, SVMs have been used for binary classification scenarios, but they can be used for multiclass cases, as well. In our work, we built binary classifiers using the SVM methods from the LIBSVM package [15][47]. We integrated several LIBSVM functions to our hardware implementation and used the LIBSVM tool as a point of reference for SVM translation to hardware. However, there are many other open source SVM implementations, such as the SMO variant and the L2-loss linear methods implemented in the Weka library [16].

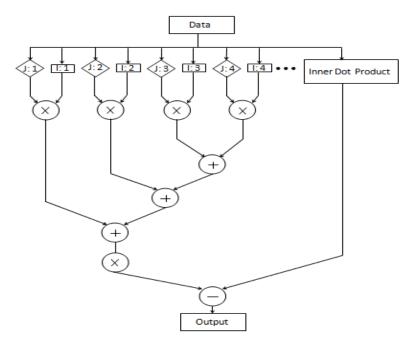

Note that quadratic programming optimization problems are computationally expensive. In cases where the datasets are high-dimensional and voluminous, such as in text classification, the kernel and inner product computations require a massive number of matrix-vector operations. On hardware however, these operations can be performed in parallel and produce the same outcomes much faster.

#### 4.5 LDA

QualiMaster uses social networks, news articles and other sources in order to gather data that can assist in financial risk analysis. A basic information retrieval method for documents is Latent Dirichlet Analysis (LDA). LDA is used in order to associate each document with a number of topics, generated at the training phase, with a certain probability for each topic. Techniques like Latent Dirichlet Analysis (LDA)[19] can be employed for uncovering the latent semantics of corpora, basically extracting the meaning of words in the corpora. Latent Dirichlet allocation identifies a given number of |Z| topics within a corpus. Being the most important parameter for LDA, this number determines the granularity of the resulting topics. In order to find the latent topics, LDA relies on probabilistic modeling. This process can be described as determining a mixture of topics z for each document d in the corpus, i.e., P(z|d), where each topic is described by terms w following another probability distribution, i.e., P(w|z).

By applying LDA latent topics as a list of terms with a probability for each term indicating the membership degree for the topic can be represented. Furthermore, for each document in the corpus LDA can determine through topic probabilities P(zj|di) regarding which topics the document belongs to and to which degree. The model needs to be trained on an example dataset and can be applied to any document later assigning the probabilities of topics to occur in that document. The training phase of LDA was considered to be implemented in hardware as it involves multiple iterations through the corpus in order to extract the topics of a dataset. The training phase's computations scale with the size of the dataset. FPGAs can be used in order to process the data in parallel, and thus reduce the execution time.

© QualiMaster Page 23(of 66)

# 5 Algorithm Analysis for Hardware Implementation

The first step to map an algorithm to hardware is to analyze it accordingly. This section describes the analysis methodology and how it was applied to the selected algorithms. Using this analysis designer will create the first hardware model with the I/O study and proper data structures. This model is the intermediate level between algorithm and actual hardware design.

# 5.1 Analysis Methodology

An algorithm, that the designer want to translate in hardware, has to be analyzed for several characteristics from the designer point of view. Inputs and outputs of the algorithm, performance issues and the basic data structures and operations are the most important. In addition, the communication overhead for the synchronization of the portions of the algorithm which run in specialized hardware with the aspects that run in software has to be considered, as excessive fragmentation may lead to poor performance (e.g. too many forks/joints for little work done in hardware). Performance issues are very important in the scope of QualiMaster, as performance quality tradeoff is of main importance as it has been analyzed in D 2.1.

#### 5.1.1 Study of Inputs and Outputs

Every algorithm has a set of inputs that are needed to be calculated to produce a set of outputs. Inputs and Outputs define the interface between the computational system and the user.

Inputs study consists of the data volume, their width, their nature, their source, and if there are used more than one time in the calculations. Volume could be the most important parameter for the study of the algorithm as it can lead to very important decisions, such as use of memory, number of processing units etc. If input data is very little then the system does not need any special handling for them as internal resources can handle them. If input data becomes bigger, and internal memory is not enough for handling their volume, then internal structures should be designed in order to compress or encode data, and, finally if volume of data is big, that reconfigurable device cannot store them, then an system e.g. external memory based system for buffering or swapping, should be designed to manipulate them. Data size is little or big depending on the target reconfigurable technology and device which is used from the designer.

The size and the characteristics of the input are important as for example if it is very large, and comes through conventional protocols (Ethernet, PCI etc) then special data structures should be designed to reassemble data. Such structures can be shift registers, very long word registers etc., which handle input data and reform them to the appropriate format for reconfigurable hardware processing.

The input data rate is also an important aspect to a system design. If the algorithm handles input data in burst mode data structures as FIFOs should be designed. If there is input data that an algorithm uses more than one time then the corresponding data structures, as cashing schemes, cyclic buffers, local memories, should also be used.

It is also important, for the designer, to study the if there is a need to design the controller for the protocol that the inputs may follow. If this system, for example, is directly connected to network with TCP/IP for streaming inputs, or an external DDR memory for large databases etc. The proper controller in hardware should be designed and integrated to the system.

The designer handles outputs similarly to the inputs. For QualiMaster scope Input and Output study is critical as it handles streaming data. Inputs and outputs have been often proved to be a

Page 24(of 66) www.qualimaster.eu

critical issue to designers for reconfigurable hardware, constraining the system performance as I/O was the bottleneck.

#### 5.1.2 Data Sets

Application or algorithm mapping to hardware demands the appropriate data set on the design and testing procedure. Dataset should be representative accordingly to the algorithm and the way the final user will use this algorithm, in order to help designer to make the right decisions. An inappropriate data set can mislead the designer to decisions that will make the final system without the desired functionality or with low performance. Data sets are used at three design phases: at profiling, simulation and verification phase. These Data Sets are the same for the hardware and software designs but analyzed in different manner.

At profiling phase the designer must analyze the algorithm or the application in order to find the most computationally demanding part. If the data set is not proper, then the designer can focus accidentally on a different part of the code than he or she should, and as a result he/she will map to hardware an inappropriate part. The resulting system will not achieve high performance as the hardware part will not be accelerating the most demanding aspect of the algorithm.

At simulation phase, the data set has to be representative and to cover every state of the algorithm. If all states are not covered, then the system cannot be tested correctly and it will probably fail at run time.

At verification phase, proper data sets lead to proper functional verification. If the data set does not cover all cases then the system will not have been properly verified and at run time it may produce wrong results. Many times these results are very difficult to be found. The well-known 1994Intel Pentium FDIV division bug is the most the famous such case.

One solution could be to have a data set that will exhaustively test the algorithm. Such a solution is completely inapplicable in practically all cases, as due to state explosion the profiling, simulation and verification phases will take too long for testing. Such Datasets are the same used in software to show proper functionality.

#### 5.1.3 Algorithm Profiling

Designers are trying to boost software performance by mapping applications to hardware. Inmost applications, usually 10% of the code consumes the 90% of the execution time, known as the 90/10 law in this context [38]. Following this rule of thumb, designers try to focus on the most demanding computational parts of an application. This approach helps the designer to save design area as he avoids to map large and complex parts of hardware that are lightly used. This area is used to map the computational demanding parts of the algorithm more than once to have a parallel execution, and a faster run time for the application. It should be noted, however, that optimizing 90% of the execution time may still be too little, as from Amdahl's law [39], even if an infinite speedup applies to the optimizable part and there is no communication overhead, a speedup of factor 10 will be achieved at most. This is a ceiling, and even the 10X speedup can be easily evaporated when communication overhead or limited performance improvement come to place. There exist applications which have substantial speedup on some critical section but in the total execution time (including I/O and communications overhead) there was a slowdown.

Several tools are used for the algorithm performance profiling. Tools as Intel VTune or GProf can profile an algorithm a procedure or instruction level. The designer runs the algorithm with a specific data set and the tool produces a report that shows the allocation of run time to every part of the

© QualiMaster Page 25(of 66)

code. It also shows the number of times that a function has been called which may also very important depending on the designers target platform.

It is important for the designer to use representative data sets. If, for example, the dataset is really small as compared to the data sets that will be used on the final system then the system initialization for example, can demand a significant percentage of run time. If the system initialization is independent from input data size, then for a much larger data set the same initialization function will demand a much smaller percentage of the execution time. Also the data nature can affect the run time distribution to functions. Usually large data sets give the proper distribution for most application. A study of the algorithm options have to be done in order to use the data with the determined nature at profiling state.

#### 5.1.4 Important Data Structures and Operations

The next step after profiling for the designer is to locate the important data structures and operations at the computationally intensive part of the algorithm. Data structures are important as using the proper ones the computations can be in parallel. As most appropriate Data Structures for mapping at reconfigurable hardware are considered static structures, with 1 and 2 dimensions tables as the most suitable. Dynamic structures using pointers, as trees, are considered as inappropriate structures for mapping in reconfigurable hardware If for example there is a comparison of an input against many comparators working in parallel will boost design performance, but even a DFS in a binary tree is challenging to map it in hardware efficiently.

Operations are also important in order to identify how system arithmetic will be implemented. If the application uses integers, and in which range, vs. single- or double-precision floating point numbers the required hardware resources may change substantially. Identifying the arithmetic, the designer will assign the available resources in order to achieve the maximum performance.

# 5.2 Count Min (CM) Modeling

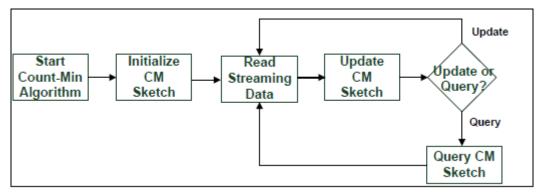

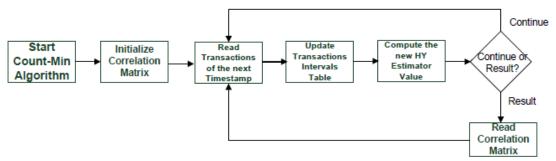

The Count-Min algorithm is based on probabilistic techniques to serve various types of queries on streaming data. The Count-Min algorithm is able to handle massive data using data structures that occupy sub-linear space vs. the size of the input dataset. The CM sketch data structure can accurately summarize arbitrary data distributions with a compact, fixed memory footprint that is often small enough to fit within cache, ensuring fast processing of updates.